ケイデンスが発表した新エコシステムがチップレット市場進化を促進

ケイデンスが発表したチップレットエコシステムの概要

ケイデンスが1月6日に発表した新しい「Chiplet Spec-to-Packaged Partsエコシステム」は、フィジカルAIやデータセンター、さらには高性能コンピューティング(HPC)のチップレット開発を加速することを目的としています。この新エコシステムは、設計の複雑さを軽減し、市場投入までの時間を短縮し、リスクを低減することを狙っています。

提携パートナーについて

ケイデンスは、Arm社、Arteris社、eMemory社、M31 Technology社、Silicon Creations社、Trilinear Technologies社といった初期IP提供パートナーとともに、半導体解析技術パートナーとしてproteanTecs社と協力しています。これにより、エコシステム全体の相互運用性が高まり、デザインの簡素化が期待されています。

チップレットプラットフォーム

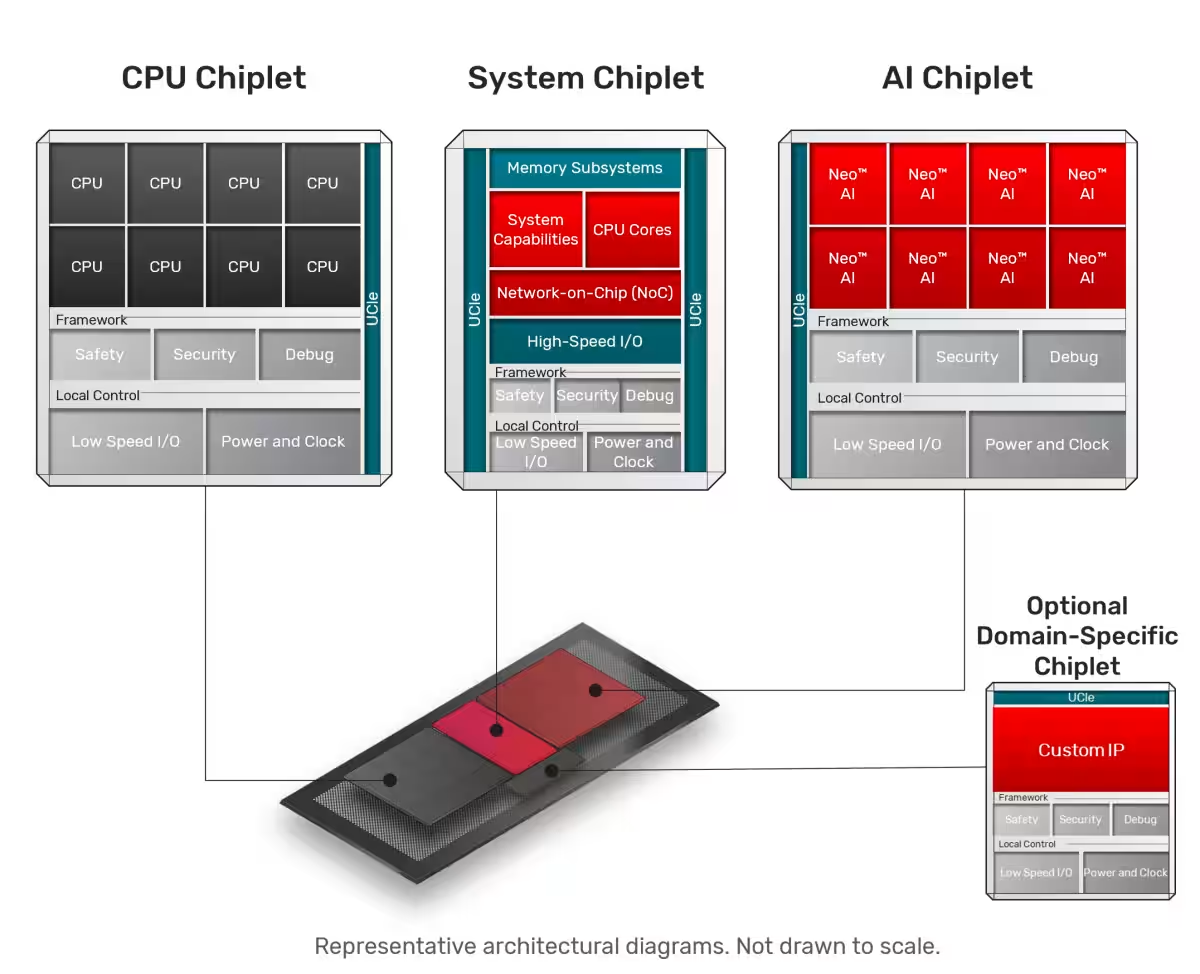

新たに提供されるCadence® Physical AIチップレットプラットフォームは、Samsung Foundryとの連携により、同社のSF5Aプロセス上で事前に統合されたIPを用いた半導体試作品のデモも行われています。このプラットフォームは、自動車やロボティクス、ドローンなどの次世代エッジAIに対応できる設計要件を満たしており、データセンターやクラウド、HPCに必要な標準I/O・メモリチップレットのニーズにも応えるものになっています。

自動化と安全性

ケイデンスは、自社およびサードパーティーによるIPを利用し、チップレット管理、セキュリティ、そして安全機能を組み込んだチップレットフレームワークアーキテクチャを構築しています。これにより、自動化が進むとともに設計の精度が向上することが期待されます。

生成されたEDAフローの革新

Cadence Xcelium™ Logic Simulatorを使用したシミュレーションと、Cadence Palladium® Z3 Enterprise Emulation Platformを用いたエミュレーションがシームレスに実現され、このフローはリアルタイムフィードバックを反映した効率的な配置配線プロセスをサポートします。これにより、設計期間の短縮と高品質な結果の両立が可能となります。

パートナー各社のコメント

Arm社

Suraj Gajendra氏は、「自動車やロボティクス分野での計算需要が高まる中、当社のArm Zena CSSを用いることで、ケイデンスのプラットフォームが次世代の要件に応えることが可能になる」と述べています。

Arteris社

Guillaume Boillet氏は、「ケイデンスのチップレットプラットフォームが、我々の高帯域幅でスケーラブルな技術と相まって次世代のアーキテクチャの採用を促進する」と期待を寄せています。

M31 Technology社

Scott Chang氏は、「ケイデンスのエコシステムに貢献できることを誇りに思っています。この協力関係を通じて、先進的なチップレットソリューションの実現が加速されるでしょう」と語っています。

まとめ

新たに発表されたケイデンスの「Chiplet Spec-to-Packaged Partsエコシステム」は、チップレット市場における設計の複雑さを減少させながら、イノベーションを促すことで、高効率かつ安全で先進的なシステムの構築に寄与することを目指しています。今後の展開に注目が集まります。

会社情報

- 会社名

- ⽇本ケイデンス・デザイン・システムズ社

- 住所

- 神奈川県横浜市港北区新横浜2-100-45 新横浜中央ビル 16階

- 電話番号

トピックス(IT)

【記事の利用について】

タイトルと記事文章は、記事のあるページにリンクを張っていただければ、無料で利用できます。

※画像は、利用できませんのでご注意ください。

【リンクついて】

リンクフリーです。