次世代AIインフラを支えるケイデンスのLPDDR6/5XメモリIP

ケイデンスが業界初のLPDDR6/5XメモリIPを発表

カリフォルニア州サンノゼを本拠とするケイデンスが、次世代AIインフラに最適化された業界初のLPDDR6/5XメモリIPシステムソリューションを発表しました。このソリューションは14.4Gbpsという高速な動作を実現し、従来のLPDDR DRAMと比べて性能が最大50%向上しています。AI負荷の高いワークロードやエンタープライズ向けの利用に最適であり、スケールアップが可能な重要なメモリ技術です。

LPDDR6/5Xの特徴と利点

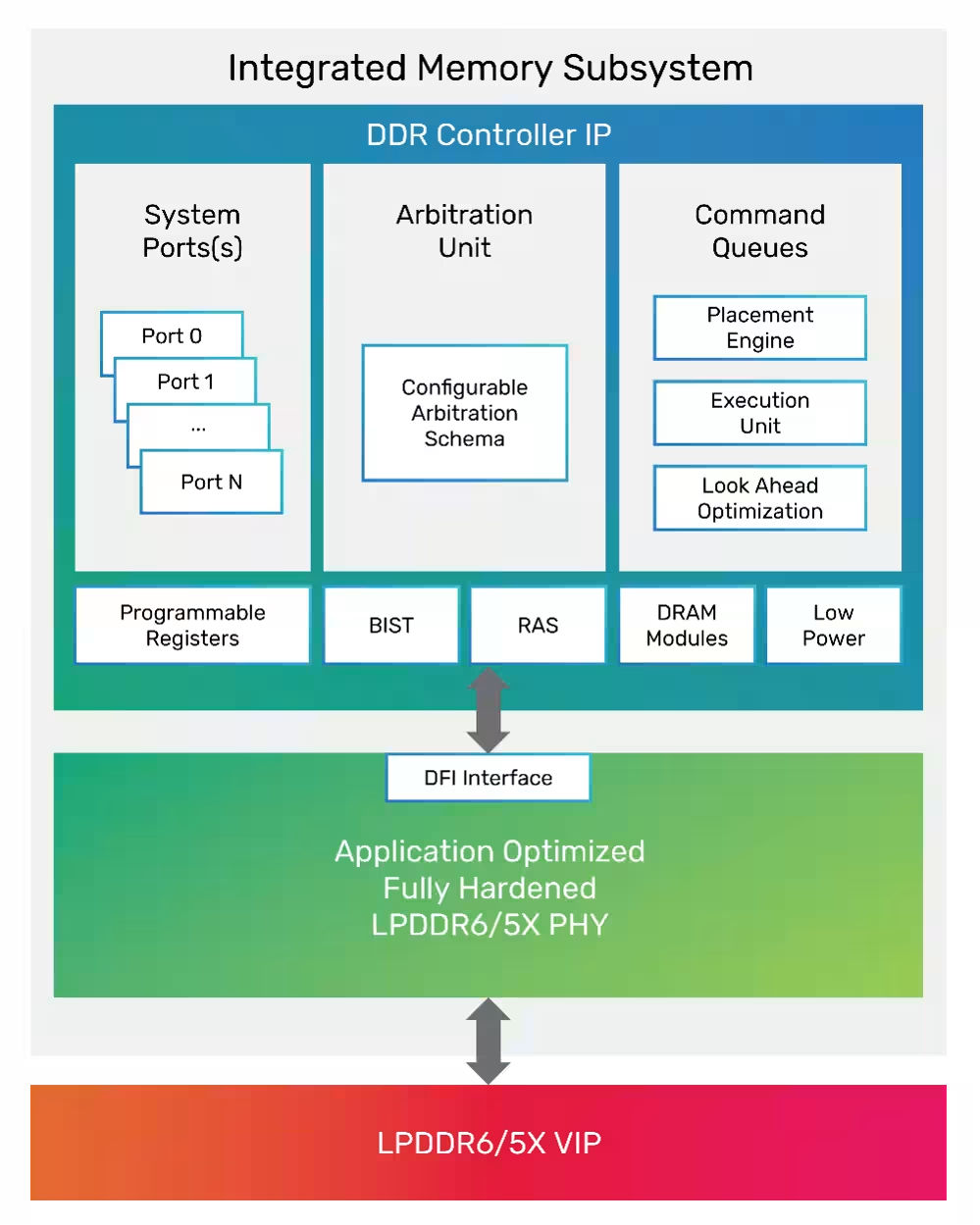

ケイデンスのLPDDR6/5XメモリIPは、電力、性能、面積(PPA)を最大化しつつ、LPDDR6とLPDDR5X DRAMプロトコルを両方ともサポートします。その設計は高度なPHYアーキテクチャと高性能なコントローラで構成され、従来のモノリシックSoCだけでなく、マルチダイシステムアーキテクチャにも対応した柔軟性を実現しています。これにより、特にAIやハイパフォーマンスコンピューティング、データセンター市場へのシームレスな統合が可能になります。

チップレットフレームワークの活用

新しいメモリIPはケイデンスのチップレットに関するフレームワークを活用しており、異なるパッケージやシステムトポロジーに対応できます。これにより、迅速かつ効率的な統合が実現し、市場への投入までの時間が大幅に短縮されます。例えば、顧客が求める特定の要件に応じて柔軟な設計が可能で、最終製品の性能やコスト目標にも幅広く対応します。

メモリコントローラの機能

CadenceのLPDDR6/5Xコントローラは、業界標準のArm® AMBA® AXIバスに対応しており、機能性、電力、面積、性能の各要素において最大級の柔軟性を提供します。これにより、エンジニアが自信を持ってメモリインターフェースを設計することが可能です。特に、LPDDR6 Memory Modelを搭載しているため、システムオンチップ(SoC)設計がJEDECインターフェース規格に適合しているかを確認でき、包括的な検証も容易に行えます。

顧客への提供状況

現在、ケイデンスは顧客との協業を進めており、LPDDR6/5X IPは同社のメモリIPシステムソリューション製品群に新たに追加した成果物です。カテゴリーにはDDR、GDDR、HBMが含まれ、幅広い市場ニーズに応える設計が行われています。さらに、UCIe™ベースのチップレットフレームワークと組み合わせることで、新しいLPDDR6/5X IPはチップレットの迅速な実現を可能にする最適化されたソリューションを提供します。

まとめ

今後、AIインフラの進化が続く中で、ケイデンスはこの新しいメモリテクノロジーのリーダーシップを発揮し、顧客のニーズに応じた最適な統合サブシステムとしてLPDDR6/5Xを提供していくでしょう。データセンターのニーズに応え、AI推論を効率的に実行するために必要な要素が、この新技術によって提供されています。詳細については、cadence.comのLPDDR特設サイトを訪れて確認してください。

会社情報

- 会社名

- ⽇本ケイデンス・デザイン・システムズ社

- 住所

- 神奈川県横浜市港北区新横浜2-100-45 新横浜中央ビル 16階

- 電話番号

トピックス(IT)

【記事の利用について】

タイトルと記事文章は、記事のあるページにリンクを張っていただければ、無料で利用できます。

※画像は、利用できませんのでご注意ください。

【リンクついて】

リンクフリーです。