スピントロニクスを活用した新たなAIハードウェアの開発

スピントロニクスを活用した新たなAIハードウェアの開発

概要

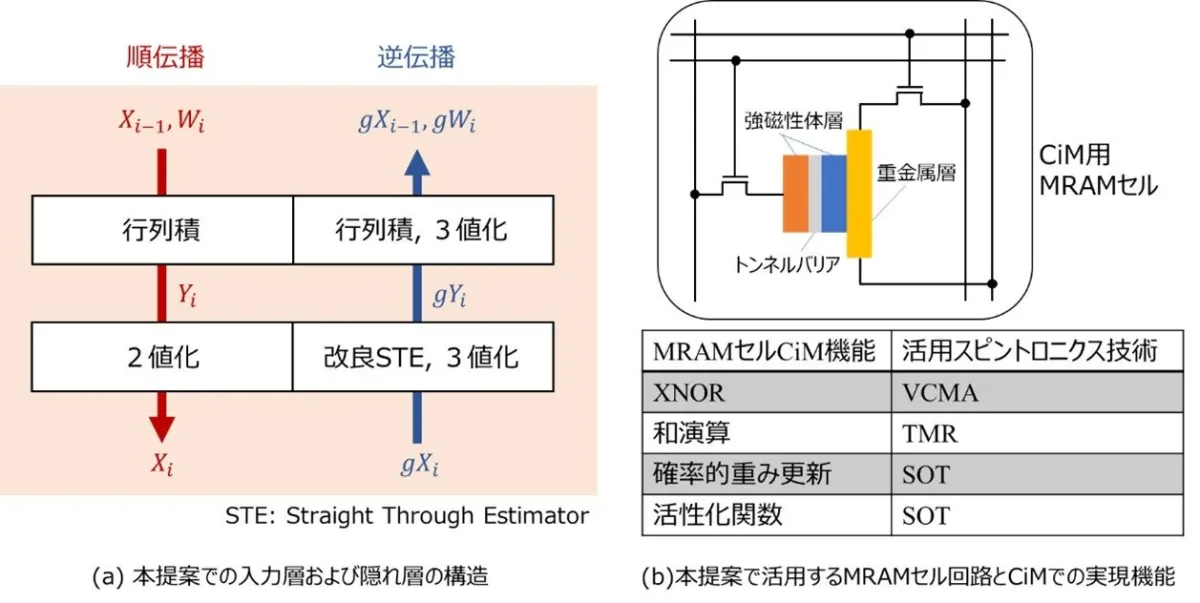

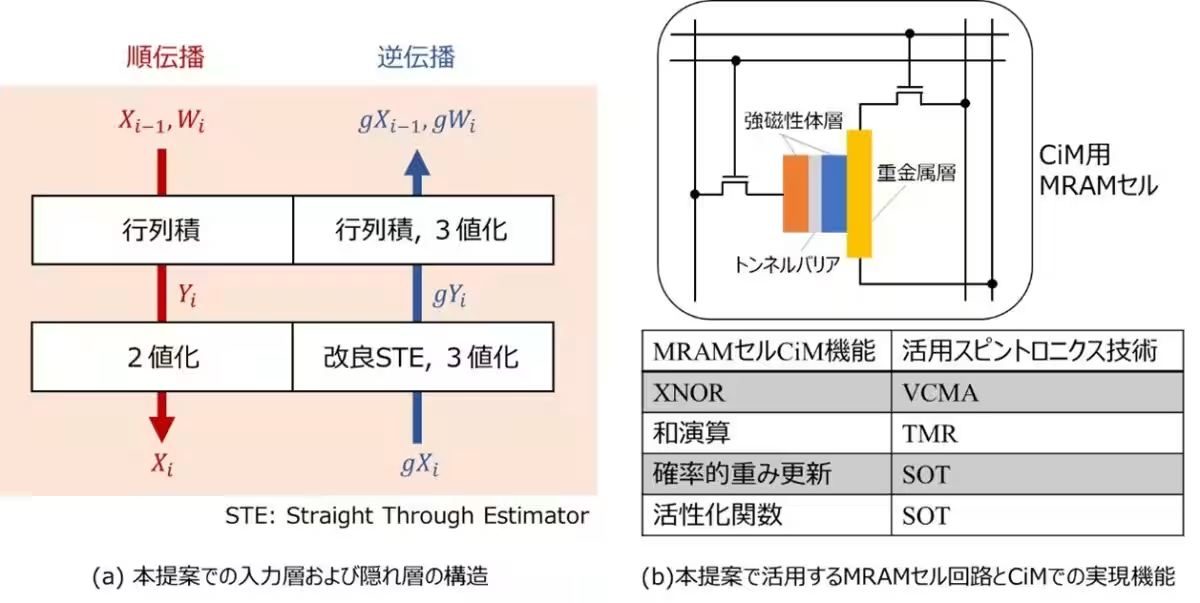

東京理科大学の河原尊之教授と大学院生の藤原優哉氏が、エッジ側における“学習機能”を持つ人工知能の実現に向けて、革新的なハードウェアを開発しました。提案されたのは三値勾配二値化ニューラルネットワーク(TGBNN)で、スピントロニクス技術を活かしたMRAMアレイを利用して、従来の限界を超える可能性を示しています。

研究の背景

人工知能技術の進化とともに、エッジデバイスにおける演算能力の改善が求められています。IAやIoTの普及に伴い、各デバイスにおいてリアルタイムの学習が求められ、そのためには、回路のサイズと消費電力を削減する必要があります。従来のBinarized Neural Network(BNN)は推論時に重みと活性化値を2値で扱いますが、学習時には実数を用いるため、エッジ側に学習機能を持たせるのが難しいという課題がありました。

三値勾配二値化ニューラルネットワーク(TGBNN)の提案

この課題を乗り越えるために、TGBNNが提案されました。TGBNNは、学習時に3値(−1、0、+1)を利用しながら、重みは2値のまま更新します。これにより、演算処理の効率が向上し、消費電力も抑えられます。さらに、スピントロニクス技術を活用してMRAMとの統合を実現したことで、従来のBNNよりも高い性能が期待されます。

性能評価

MRAMアレイを用いた実験によって、88%以上の精度が確認されました。厳密に設計された新たなアルゴリズムは、学習時の勾配を3値化し、MRAM内での演算を効率化しています。これにより、エッジデバイス上でも学習機能を保持したBNNが実現可能となります。

技術的アプローチ

具体的には、以下の3つの技術要素が重要です:

1. 3値勾配を用いた新たな学習アルゴリズム: 学習過程での勾配を3値化することで、計算の精度引き上げを図ります。

2. MRAMセルによるXNORゲートの実装: スピントロニクス技術を用いて、新たなゲートを実現し、より効率的な学習回路を作成しました。

3. MRAMアレイ上でのBNN学習アルゴリズムの実行: 提案されたアルゴリズムをMRAMアレイに実装することで、回路の規模を削減しつつ必要な学習機能を保持しました。

今後の展望

この研究成果は、次世代のAI技術の発展に寄与する可能性が高く、エッジデバイスでの活用が期待されています。特に、スピントロニクス技術の導入は、新たなコンピューティングアーキテクチャの方向性を示しており、今後の研究や商業利用において重要なステップといえるでしょう。

まとめ

東京理科大学によるこの研究は、AIテクノロジーをエッジ側にもたらす重要なマイルストーンです。スピントロニクスを活用した新たなアプローチは、今後の人工知能の発展を加速させるものであり、さらなる研究の進展が期待されます。

会社情報

- 会社名

- 学校法人東京理科大学

- 住所

- 東京都新宿区神楽坂1-3

- 電話番号

- 03-3260-4271

トピックス(科学)

【記事の利用について】

タイトルと記事文章は、記事のあるページにリンクを張っていただければ、無料で利用できます。

※画像は、利用できませんのでご注意ください。

【リンクついて】

リンクフリーです。