神戸大学とPFN共同開発のMN-Core™が世界的性能を誇るスパコンに進化

MN-Core™がもたらした新たな計算力

神戸大学と株式会社Preferred Networks(以下、PFN)によって共同開発されたディープラーニングプロセッサー『MN-Core™』が、最新のスパコン省電力ランキング「Green500」で堂々の世界一を獲得しました。この成果は、最新のLSI(大規模集積回路)設計技術を駆使したアルチップの支援があったからこそ実現したものです。

MN-Core™の革新性

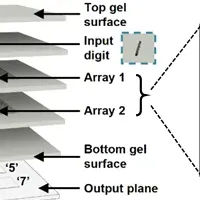

『MN-Core™』は、800mm²の広大なLSIダイを4つ接続した革新が特徴です。アルチップが誇るチップ間インターフェース技術を使用し、これを1パッケージ内にまとめて実装しています。特に注目すべきは、TSMC(台湾積体電路製造)のプロセスを採用し、512個の演算ブロックを内蔵、半精度浮動小数点数演算を駆使して理論上の1TFLOPS/Wの電力効率を実現している点です。

計算機クラスタ「MN-3」の実力

PFNの「MN-3」は、MN-Core™を計算アクセラレーターとして搭載した計算機クラスタです。GPGPUを使用した「MN-2」とともに、JAMSTEC横浜研究所に設置され、46ノードでの稼働を開始しています。計算ノードにはMN-Coreが4つ組み込まれ、40ノードを使用したGreen500の測定では、1Wあたり21.11GFLOPSという驚異的な計算速度を記録しています。この数値は、電力効率を最大限に引き上げた結果であり、市場における競争力を更に高める要因となっています。

アルチップの技術と挑戦

『MN-Core™』の開発には多くの技術的な挑戦が伴いました。アルチップのCEO、Johnny Shen氏は、「様々な要求や課題に対策しつつ、独自技術を用いた結果、期待通りの仕様で完成に至った」と語っています。特に注目されるのは、巨大なダイを用いたクロック設計技術や熱対策、試験体制の確立です。

独自技術の数々

- - ユニークなクロック設計技術: バラつきを回避し、効率的な電力削減を実現。

- - 4つのダイを実装したパッケージ: 85x85mmのサイズに約6400個のボール数を誇り、慎重に開発されたメカニカルデザインで取り扱いを安定化。

- - プロセッサコアの繰り返し構成: 信頼性とテスト品質を確保するため、独自テスト回路を設計。

- - ダイ間のインターフェース接続: オリジナルのD2D接続技術によって、最小のエリアで最大限の電力効率を実現。

企業からのコメント

PFNの執行役員、土井裕介氏は「アルチップの技術は、MN-Core™の開発において不可欠だった」とコメントしています。また、TSMCの代表取締役社長、小野寺誠氏も「日本のディープラーニング分野における研究開発を支援できて光栄」と述べています。

会社概要

アルチップ・テクノロジーズ・リミテッドは、2003年に設立された台湾の企業で、ASIC/SoCの設計及び製造に特化したサービスを提供しています。神奈川県横浜にもオフィスを構えており、今後もディープラーニング分野における発展に寄与していく予定です。

- - 会社名: アルチップ・テクノロジーズ・リミテッド

- - 所在地: 台湾台北、横浜市港北区新横浜

- - 代表: Johnny Shen (CEO)

この取り組みは、今後のAI技術の進化に大きな影響を与えると予想されています。未来の技術革新から目が離せません。

会社情報

- 会社名

- アルチップ・テクノロジーズ株式会社

- 住所

- 神奈川県横浜市港北区新横浜2-3-12新横浜スクエアビル 10F

- 電話番号

- 045-470-1090

関連リンク

サードペディア百科事典: 兵庫県 神戸市 Preferred Networks MN-Core™ アルチップ

Wiki3: 兵庫県 神戸市 Preferred Networks MN-Core™ アルチップ

トピックス(科学)

【記事の利用について】

タイトルと記事文章は、記事のあるページにリンクを張っていただければ、無料で利用できます。

※画像は、利用できませんのでご注意ください。

【リンクついて】

リンクフリーです。