次世代パワー半導体の実証成功: r-GeO₂ MOSFETの新たな時代へ

次世代パワー半導体の実証成功: r-GeO₂ MOSFETの新たな時代へ

2026年3月31日、Patentix株式会社はルチル型二酸化ゲルマニウム(r-GeO₂)を用いたデプレッション型MOSFETのトランジスタ動作の実証に成功したと発表しました。この成果は、特に次世代パワー半導体材料として大きな期待を寄せられているr-GeO₂が持つ特性を最大限に活かしたものです。

ルチル型二酸化ゲルマニウム(r-GeO₂)とは

r-GeO₂は、従来の半導体材料である炭化ケイ素(SiC)や窒化ガリウム(GaN)よりも大きなバンドギャップ(4.68 eV)を持ち、p型およびn型の両方の伝導性が理論的に可能とされています。そのため、高耐圧・高出力・高効率なパワー半導体デバイスの実現が期待されています。

Patentixでは、これまでにSbをドーパントとしたn型r-GeO₂の成膜技術や導電性制御技術を確立し、ショットキーバリアダイオードの動作確認を行ってきました。MOSFETの実現に向けた道筋が見え始めています。

先行研究と課題

r-GeO₂に関する先行研究として、スパッタ成膜技術を用いてSiO₂/p+ Si基板上にGeO₂膜を形成し、FET動作が示された事例があります。また、2025年にはTSSG法を用いて育成されたr-GeO₂の単結晶へのリンのイオン注入によるMOSFETの動作も報告されました。しかし、ヘテロエピタキシャル膜を用いたMOSFETの実証はこれまでなされていませんでした。

成果の詳細

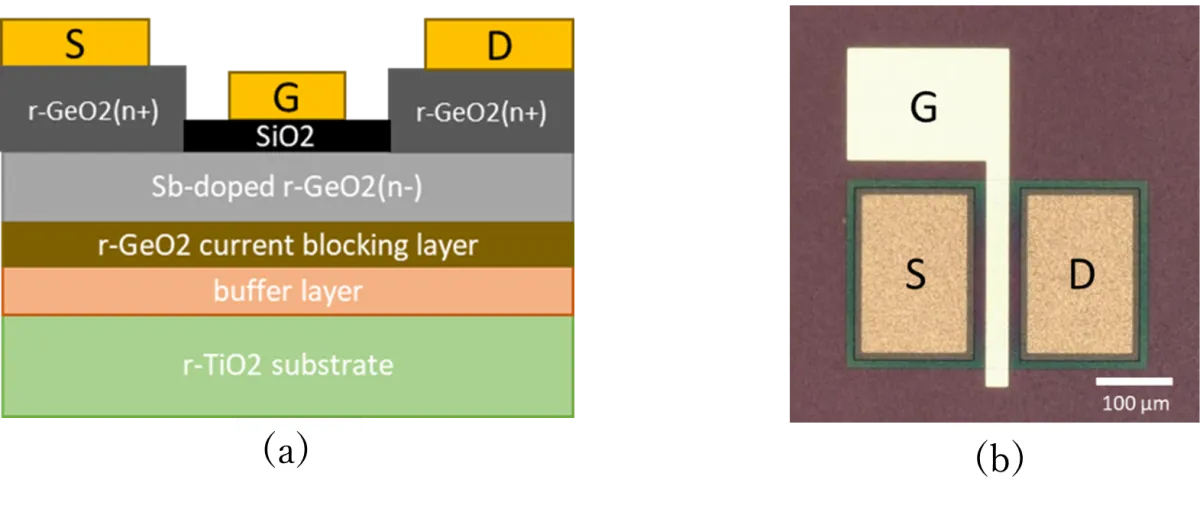

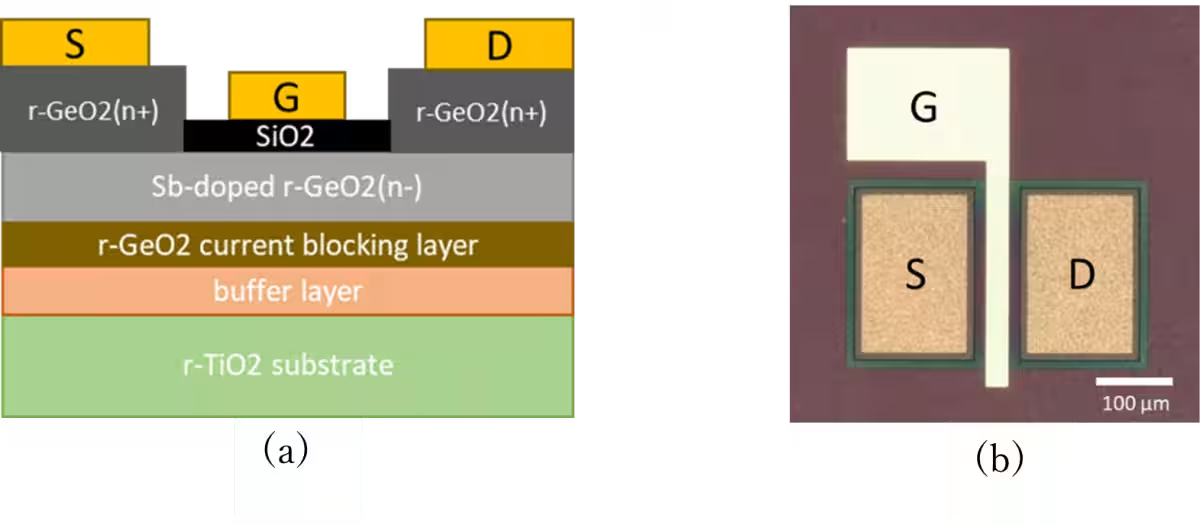

今回の成果により、Patentixはn型r-GeO₂のみで作成可能なデプレッション型MOSFETのトランジスタ動作を実証しました。作製されたMOSFETの概略図は以下の通りです。

新たなデバイス構造においては、r-TiO₂基板上にドーピングしたr-GeO₂膜が電流遮断層を形成し、その上にSbドープn型チャネル層とソース/ドレインのn+層が成膜されました。ゲート絶縁膜にはSiO₂(厚さ75nm)が使用され、電極にはPt/Tiが選択されています。

このモデルでは、負のゲート電圧を印加することでドレイン-ソース間の電流を遮断できる特性が確認されました。

性能特性

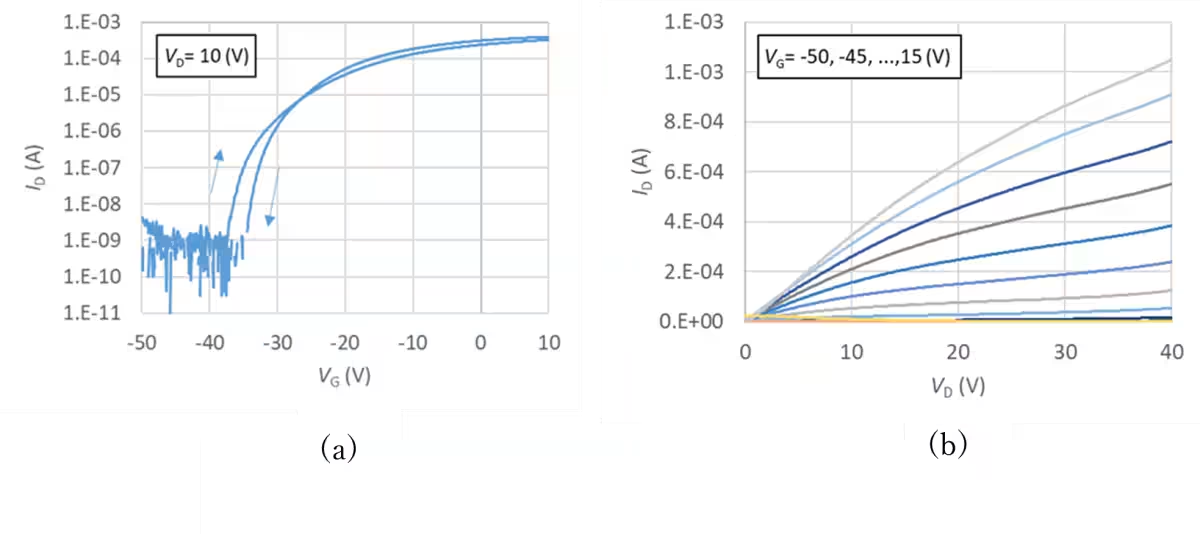

デバイスの特性評価の結果、ゲート電圧VGの変化に伴い、ドレイン電流IDが5桁以上の大きなオン/オフ比で変化することが確認されました。具体的には、図2(a)に示すようなID-VG特性を有し、負のゲート電圧ではドレイン電流がオフになります。

また、図2(b)では、ドレイン電圧Vdの増加に対して特性が線形から飽和特性へ移行する様子も確認されました。この特性により、r-GeO₂ MOSFETが持つ優れた電流特性が示されています。

将来の展望

今後、Patentixではr-GeO₂のパワー半導体材料としての信頼性を高めるために、p型r-GeO₂の作製技術をさらに確立し、エンハンスメント型MOSFETの動作実証に向けた研究開発を進めていきます。この取り組みは、エレクトロニクス産業における革新を促進する重要なステップとなるでしょう。

この実証成功は、半導体業界における新たなスタンダードを示唆するものであり、未来のエネルギー効率の改善やデバイスの高性能化に貢献することが期待されます。

会社情報

- 会社名

- Patentix株式会社

- 住所

- 滋賀県草津市野路東1丁目1番1号立命館大学BKCインキュベータ

- 電話番号

- 0775-99-1558

トピックス(IT)

【記事の利用について】

タイトルと記事文章は、記事のあるページにリンクを張っていただければ、無料で利用できます。

※画像は、利用できませんのでご注意ください。

【リンクついて】

リンクフリーです。